#### Hardware

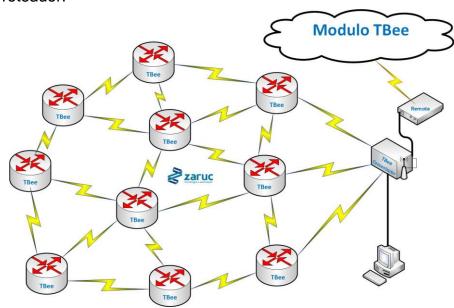

O TBEE - modulo transceptor TAD OEM com certificação Anatel destinado à comunicação sem fio na frequência de 2.4 GHz, podendo estabelecer a comunicação em diferentes topologias de rede, dentre elas estrela, árvore e malha.

"Este equipamento opera em caráter secundário, isto é, não tem direito à proteção contra interferência prejudicial, mesmo de estações do mesmo tipo, e não pode causar interferência a sistemas operando em caráter primário."

#### Descrição do funcionamento

O TBEE é fornecido com *firmware* padrão que permite a formação de uma rede *ZigBee* em malha, também denominada *mesh*. Fornecido com dois *firmwares* distintos: TBee coordenador e TBee roteador.

O coordenador possui a tarefa de controlar e gerenciar a rede, rotear quadros, permitir associação de novos dispositivos, endereçar os dispositivos em muitas e, aplicações, é o elemento da rede para o qual se concentra todo o fluxo de dados. Com a exceção da formação e controle da rede, o roteador possui as mesmas funcionalidades do coordenador. Diante disto, para a formação da rede é obrigatória presença do dispositivo coordenador, que estando ligado na mesma área

de cobertura de um ou mais roteadores, estabelece os enlaces de comunicação.

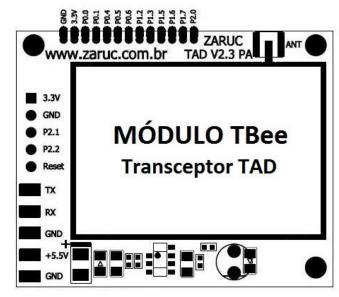

## Módulo TBEE PA - 1100m - Anatel 3314-11-7453

# Especificação Técnica

| Unidade de RF |                                       |                                      |

|---------------|---------------------------------------|--------------------------------------|

|               | Frequência                            | 2400 - 2485 Mhz                      |

|               | Modulação                             | O-QPSK                               |

|               | Potência Saída                        | 18 dBm                               |

|               | Sensibilidade                         | -98,5 dBm                            |

|               | Taxa máxima                           | 250 kbps                             |

|               | Corrente de pico                      | 130 mA                               |

|               | Corrente nominal                      | 32 mA                                |

|               | Distância máxima (com visada)         | 1100 m                               |

|               | Temperatura de operação               | -40 a 85 ºC                          |

|               | Antena                                | Conector u.FL + Antena 2 dBi incluso |

|               | Impedância                            | 50 ohms                              |

| μControlador  |                                       |                                      |

|               | Família                               | CC2530 (núcleo Intel 8051)           |

|               | Memória RAM                           | 8 KB                                 |

|               | Memória FLASH                         | 256 KB                               |

| UART          |                                       |                                      |

|               |                                       | UART1                                |

|               | Quantidade                            |                                      |

|               |                                       | UART2                                |

|               | Baud rate                             | 110 - 115200 bps                     |

|               | Nível de Sinal                        | TTL CMOS 3.3 V                       |

|               | Canais de DMA                         | 1 - UART1                            |

| SPI           |                                       |                                      |

|               | Quantidade                            | 1 - Compartilhado com UART2          |

|               | Frequência máxima                     | 4 Mhz                                |

| GPIO          | ·                                     |                                      |

|               | Quantidade                            | 10                                   |

|               | Nível de Sinal                        | TTL CMOS 3.3 V                       |

| Alimentação   |                                       |                                      |

| <u>-</u>      | Range                                 | 3.3 a 5.5 V DC                       |

|               | Corrente máxima                       | 130 mA                               |

| Dimensões     | 37 x 30 x 4 mm (A x L x P)            |                                      |

|               | · · · · · · · · · · · · · · · · · · · |                                      |

### Descrição dos terminais

| GND    | Referência                                                     |

|--------|----------------------------------------------------------------|

| +5.5 V | Alimentação através do regulador LDO. Range de 3.3 a 5.5 V DC  |

| RX     | RX - UART1                                                     |

| TX     | TX - UART1                                                     |

| RESET  | Reset do μC. Ativo em nível lógico baixo.                      |

| P2.2   | Terminal de gravação (DC - debug clock)                        |

| P2.1   | Terminal de gravação (DD - debug data)                         |

| 3.3V   | Alimentação direta ao μC                                       |

| P0.0   | I/O                                                            |

| P0.1   | I/O                                                            |

| P0.4   | Desacoplamento da UART1. Nível lógico alto desabilita RX UART1 |

| P0.5   | I/O                                                            |

| P0.6   | I/O, SPI_CSS                                                   |

| P1.2   | I/O                                                            |

| P1.3   | I/O                                                            |

| P1.5   | I/O, SPI_CLK                                                   |

| P1.6   | I/O, TX - UART2, SPI_MOSI                                      |

| P1.7   | I/O, RX - UART2, SPI_MISO                                      |

| P2.0   | I/O                                                            |

|        | ·                                                              |